- 您现在的位置:买卖IC网 > Sheet目录362799 > EVAL-AD1928EB (Analog Devices, Inc.) 2 ADC/8 DAC with PLL, 192 kHz, 24-Bit Codec

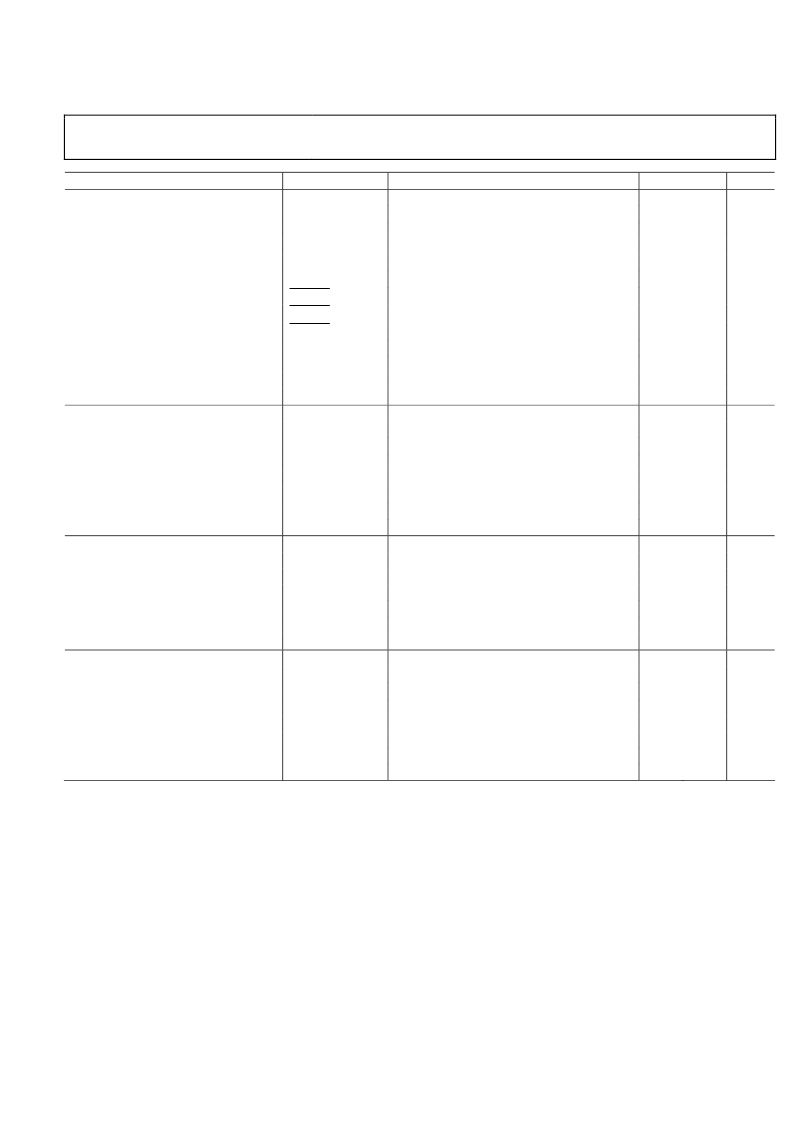

AD1928

Parameter

SPI PORT

t

CCH

t

CCL

f

CCLK

t

CDS

t

CDH

t

CLS

t

CLH

t

CLHIGH

t

COE

t

COD

t

COH

t

COTS

DAC SERIAL PORT

t

DBH

t

DBL

t

DLS

t

DLH

t

DLSKEW

t

DDS

t

DDH

ADC SERIAL PORT

t

ABH

t

ABL

t

ALS

t

ALH

t

ALSKEW

t

ABDD

AUXILIARY INTERFACE

t

AXDS

t

AXDH

t

DXDD

t

XBH

t

XBL

t

DLS

t

DLH

Rev. 0 | Page 7 of 32

Condition

CCLK high

CCLK low

CCLK frequency

CIN setup

CIN hold

CLATCH setup

CLATCH hold

CLATCH high

COUT enable

COUT delay

COUT hold

COUT tristate

DBCLK high

DBCLK low

DLRCLK setup

DLRCLK hold

DLRCLK skew

DSDATA setup

DSDATA hold

ABCLK high

ABCLK low

ALRCLK setup

ALRCLK hold

ALRCLK skew

ASDATA delay

AAUXDATA setup

AAUXDATA hold

DAUXDATA delay

AUXBCLK high

AUXBCLK low

AUXLRCLK setup

AUXLRCLK hold

Comments

See Figure 11, except where otherwise noted

f

CCLK

= 1/t

CCP

, only t

CCP

shown in Figure 11

To CCLK rising

From CCLK rising

To CCLK rising

From CCLK falling

Not shown in Figure 11

From CCLK falling

From CCLK falling

From CCLK falling, not shown in Figure 11

From CCLK falling

See Figure 24

Slave mode

Slave mode

To DBCLK rising, slave mode

From DBCLK rising, slave mode

From DBCLK falling, master mode

To DBCLK rising

From DBCLK rising

See Figure 25

Slave mode

Slave mode

To ABCLK rising, slave mode

From ABCLK rising, slave mode

From ABCLK falling, master mode

From ABCLK falling

To AUXBCLK rising

From AUXBCLK rising

From AUXBCLK falling

To AUXBCLK rising

From AUXBCLK rising

Min

35

35

10

10

10

10

10

30

10

10

10

5

8

10

5

10

10

10

5

8

10

5

10

10

10

5

Max

10

30

30

30

+8

+8

18

18

Unit

ns

ns

MHz

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EVAL-AD1938EB

4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

EVAL-AD1939EB

4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

EVAL-AD1935EB

4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

EVAL-AD1936EB

4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

EVAL-AD1937EB

4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

Eval-AD1940EB

SigmaDSP-TM Multichannel 28-Bit Audio Processor

EVAL-AD1953EB

16-bit fixed point DSP with Flash

EVAL-AD1958EB

PLL/Multibit DAC

相关代理商/技术参数

EVAL-AD1928EBZ

制造商:AD 制造商全称:Analog Devices 功能描述:2 ADC/8 DAC with PLL, 192 kHz, 24-Bit Codec

EVAL-AD1934EB

制造商:AD 制造商全称:Analog Devices 功能描述:8-Channel DAC with PLL, 192 kHz, 24 Bits

EVAL-AD1935EB

制造商:AD 制造商全称:Analog Devices 功能描述:4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

EVAL-AD1936EB

制造商:AD 制造商全称:Analog Devices 功能描述:4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

EVAL-AD1937AZ

功能描述:BOARD EVAL FOR AD1937 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源

EVAL-AD1937EB

制造商:AD 制造商全称:Analog Devices 功能描述:4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

EVAL-AD1937EBZ

制造商:Analog Devices 功能描述:EB SINGLE CHIP CODEC 4 ADC'S W/DIFF OUTP - Boxed Product (Development Kits)

EVAL-AD1938AZ

功能描述:BOARD EVAL FOR AD1938 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源